# Processamento Paralelo - I

## Canto III

### A porta do Inferno - Vestíbulo Rio Aqueronte - Caronte

POR MIM SE VAI À CIDADE DOLENTE,

POR MIM SE VAI À ETERNA DOR ,

POR MIM SE VAI À PERDIDA GENTE.

JUSTIÇA MOVEU O MEU ALTO CRIADOR,

QUE ME FEZ COM O DIVINO PODER,

O SABER SUPREMO E O PRIMEIRO AMOR.

ANTES DE MIM COISA ALGUMA FOI CRIADA

EXCETO COISAS ETERNAS, E ETERNA EU

DURO.

DEIXAI TODA ESPERANÇA, VÓS QUE ENTRAIS!

## Visão Tradicional x Paralelismo

### 1. Tradicionalmente:

- máquina sequencial

### 2. Melhorar desempenho e disponibilidade:

- paralelismo

### 3. Diversidade:

- muitos sistemas com capacidade de processamento paralelo:

- multiprocessadores simétricos

- acesso não uniforme à memória

- clusters

- multithread e chips multiprocessadores

- processadores vetoriais

- processadores matriciais

- ...

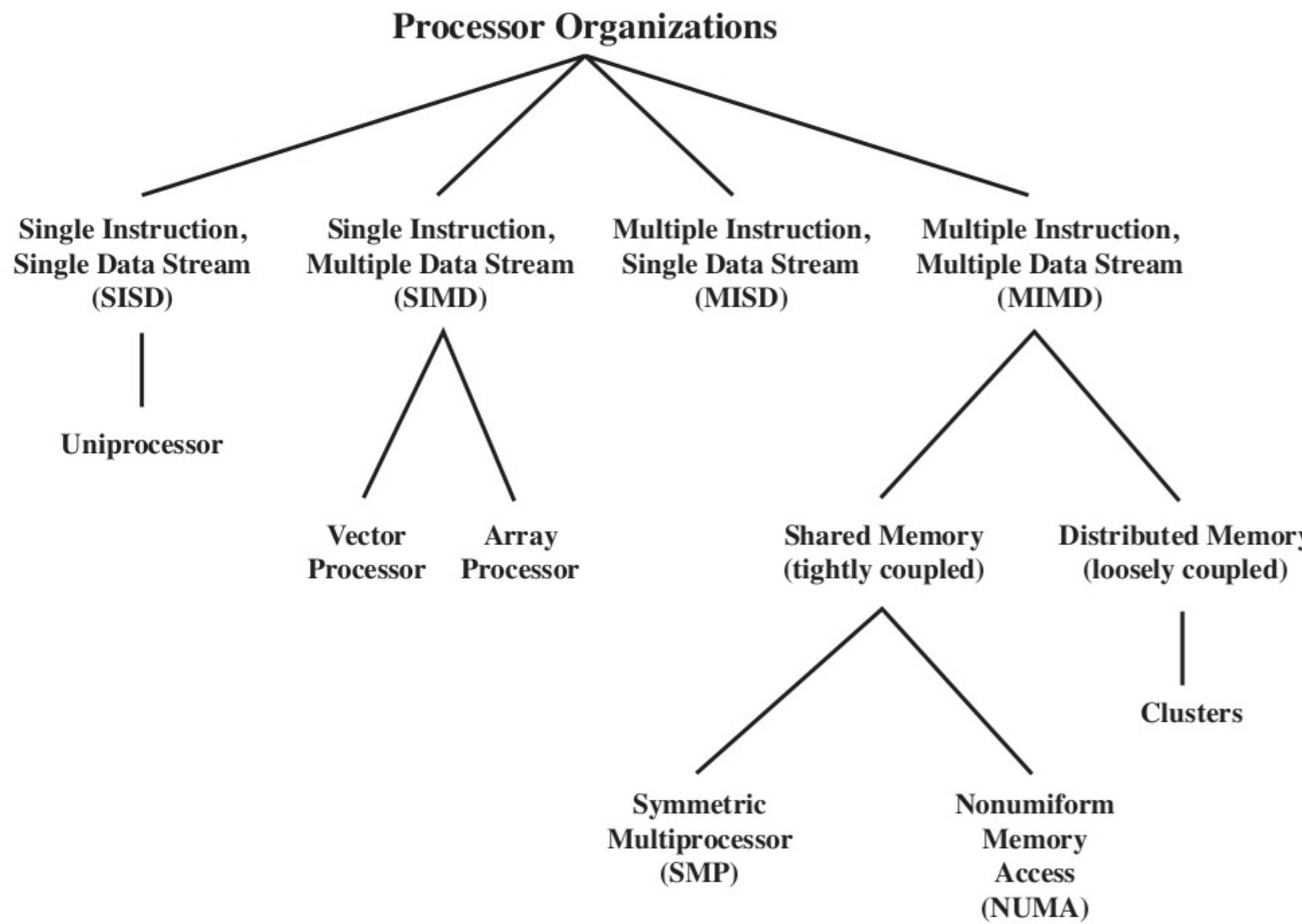

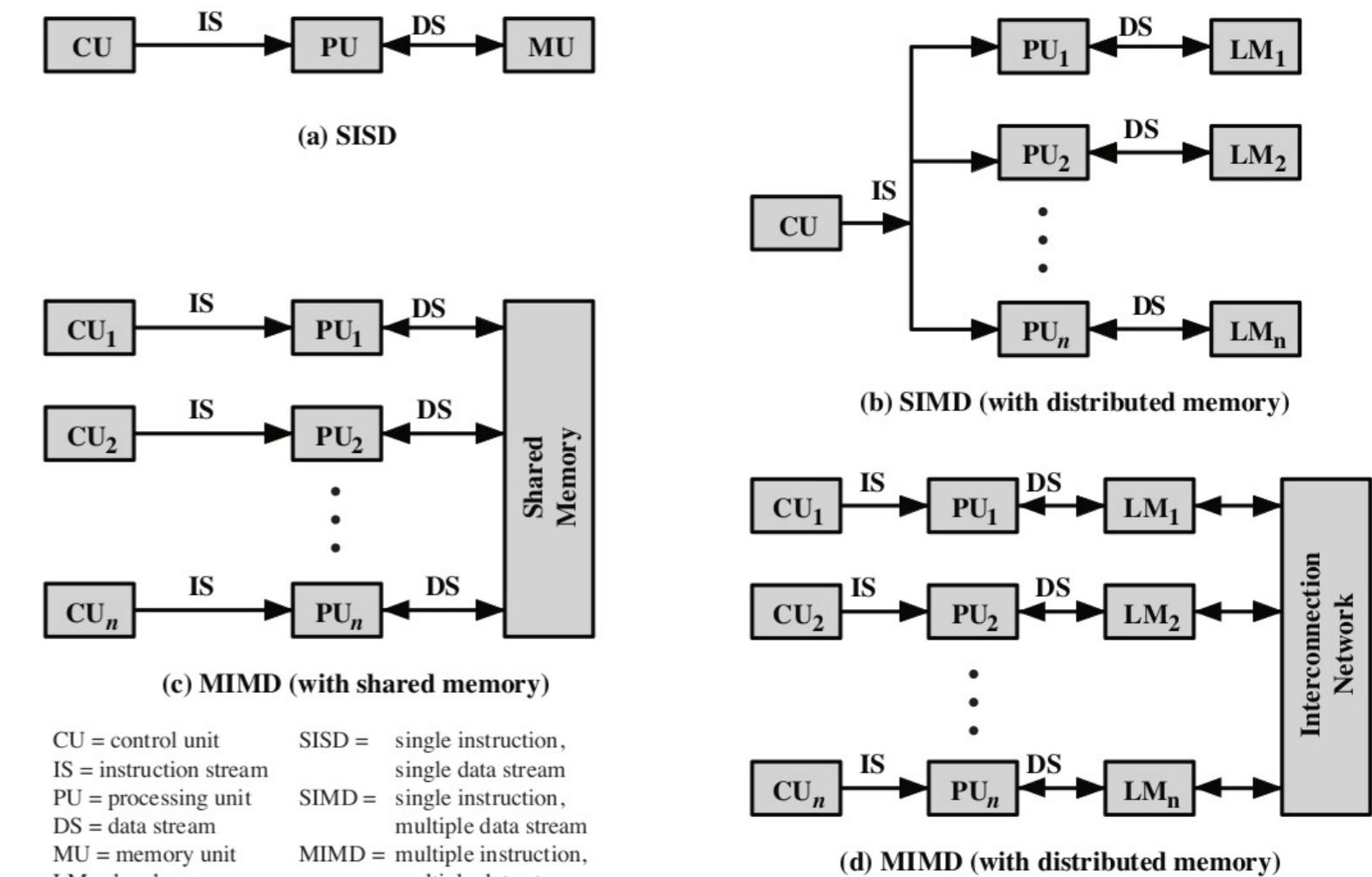

# Classificação dos Sistemas com Capacidade de Processamento Paralelo (Flynn)

**Por que é complexo?**

organização física

estruturas de interconexão

comunicação entre processadores

sistemas operacionais

softwares aplicativos

...

CU = control unit

IS = instruction stream

PU = processing unit

DS = data stream

MU = memory unit

LM = local memory

SISD = single instruction, single data stream

SIMD = single instruction, multiple data stream

MISD = multiple instruction, single data stream

MIMD = multiple instruction, multiple data stream

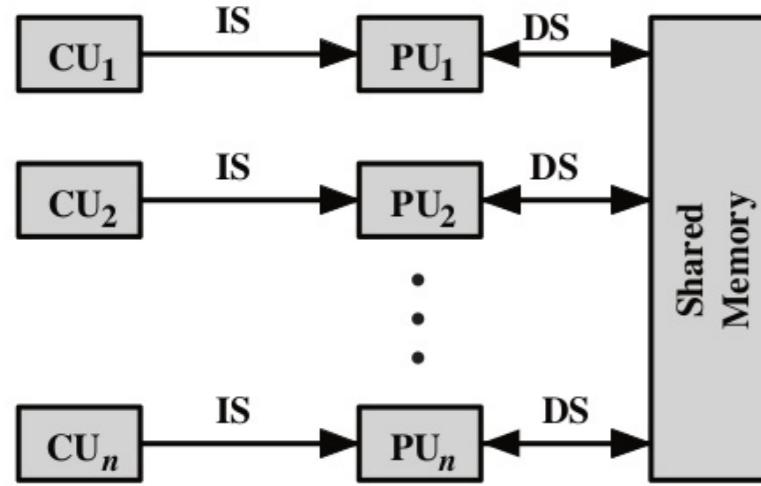

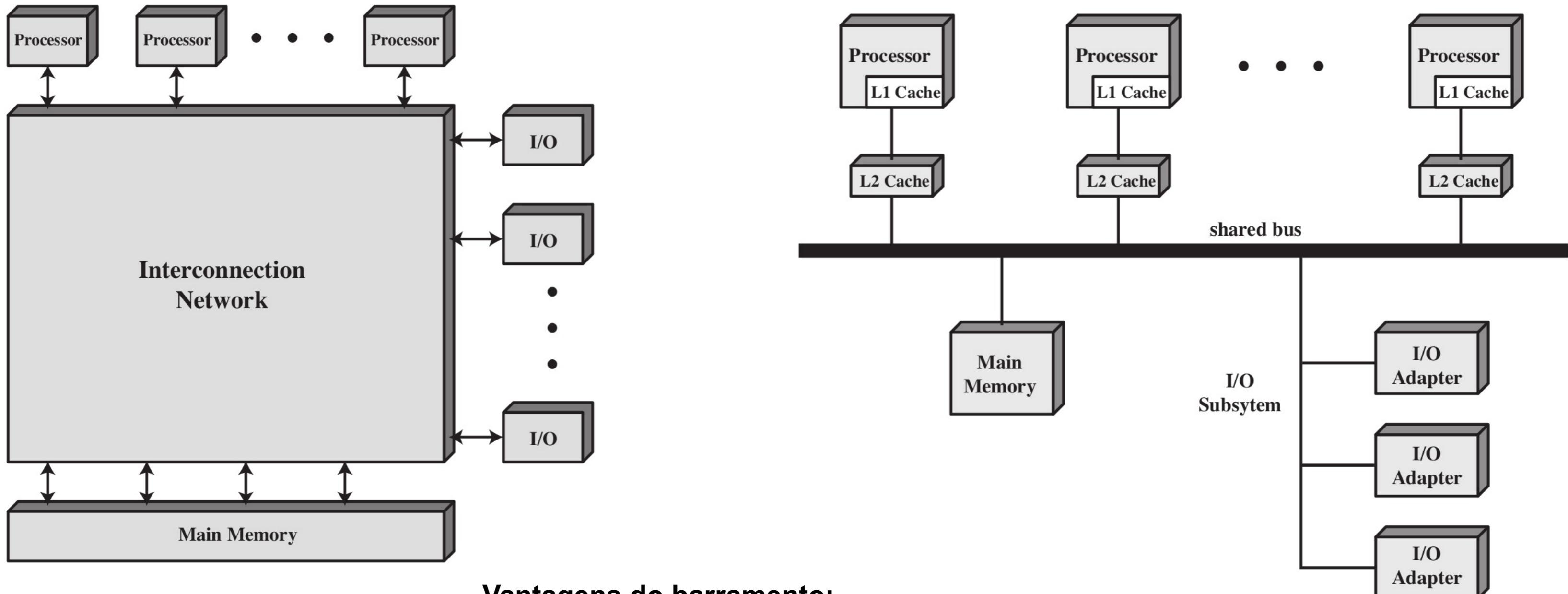

## Multiprocessadores Simétricos (SMP): conceitos

**Vantagens:**

**desempenho**

**disponibilidade**

**crescimento incremental**

**escalabilidade**

**transparência ao usuário**

**Características:**

**2 ou mais processadores semelhantes

de capacidade comparável**

**compartilham a mesma memória principal

e os recursos de I/O**

**o acesso aos dispositivos de I/O é feito

pelos mesmos canais ou por canais

diferentes que fornecem acesso aos

mesmos dispositivos**

**todos os processadores desempenham

as mesmas funções (por isso "simétricos")**

**todo o sistema é controlado por um SO que

faz a interação entre os processadores e

os programas, tarefas, arquivos etc. É o SO

que agenda os processos ou threads por

meio de todos os processadores.**

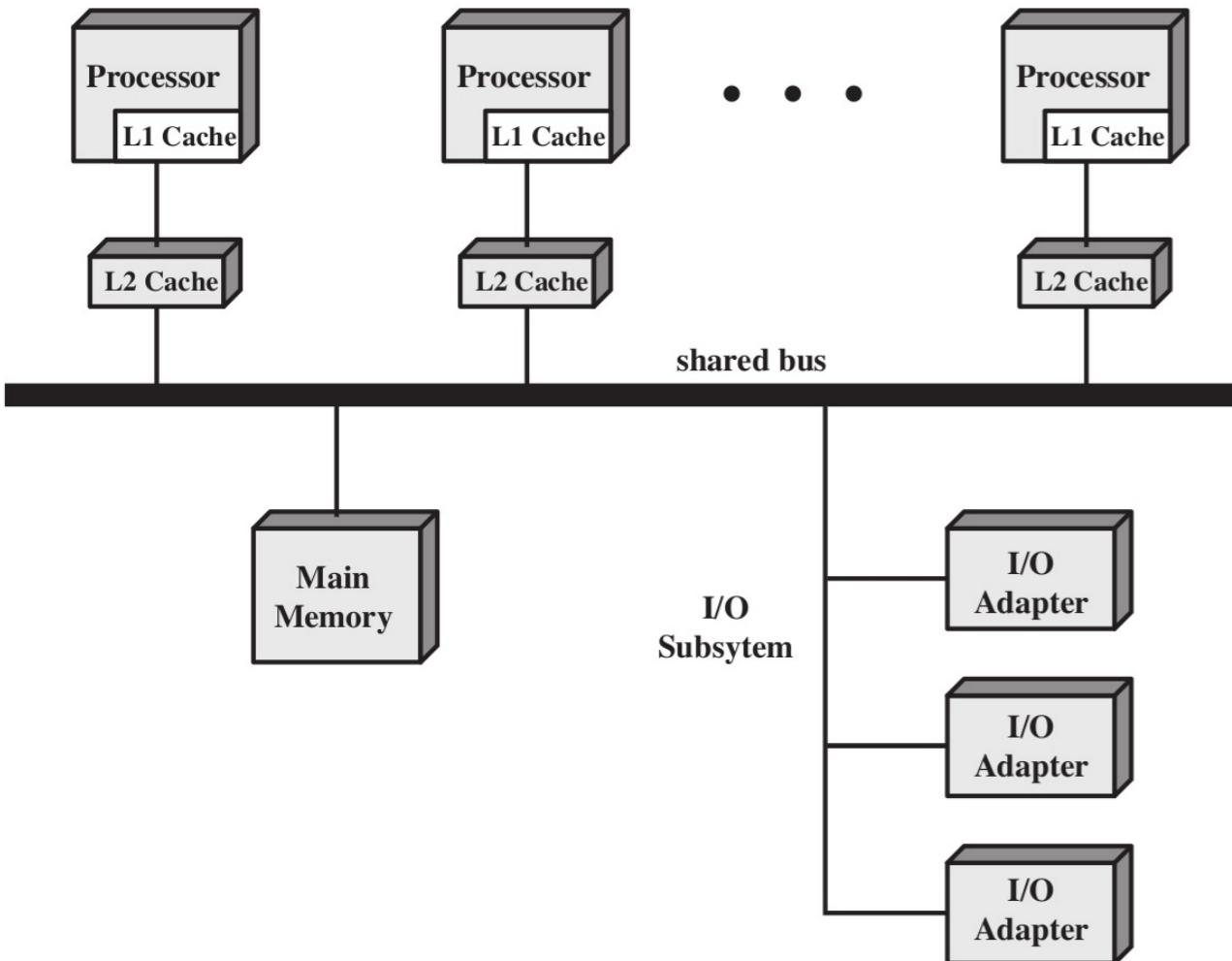

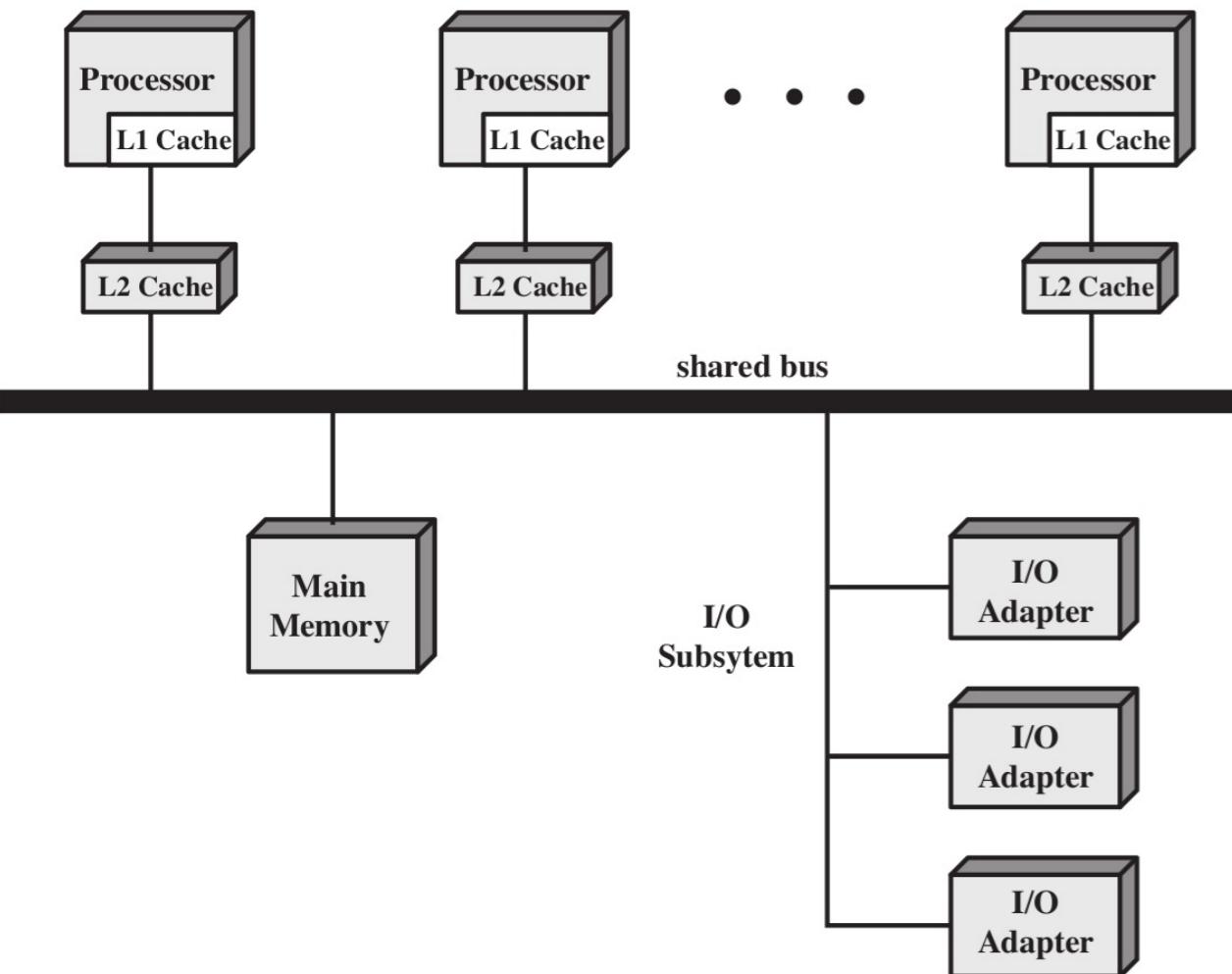

# Multiprocessadores Simétricos (SMP): organização

## Projeto de SO para SMP:

- processos concorrentes

- escalonamento

- sincronização

- gerenciamento memória

- confiabilidade/falhas

## Vantagens do barramento:

- simplicidade

- flexibilidade

- confiabilidade

## Desvantagens do barramento:

- desempenho

- coerência de cache

## Recursos do barramento de tempo compartilhado:

- endereçamento de origem/destino

- arbitração (prioridade) de requisições concorrentes

- tempo compartilhado

# Multiprocessadores Simétricos (SMP): coerência de cache

## Soluções por Software:

- evita hardware adicional

- complexidade vai para software

- abordagem comum: evitar dados compartilhados na memória cache

- abordagem sofisticada: análise de código

## Soluções por Hardware: Protocolos de Coerência de Cache

- transparente para o programador e software/compilador

- melhor desempenho

- **Protocolos de Diretório:**

- controlador central na memória

- diretório com estado global do conteúdo das caches

- **Protocolo de Monitoração:**

- responsabilidade distribuída

- mudanças devem ser anunciadas

- abordagem write invalidate: vários leitores, 1 escritor (protocolo MESI)

- abordagem write update: vários leitores e vários escritores

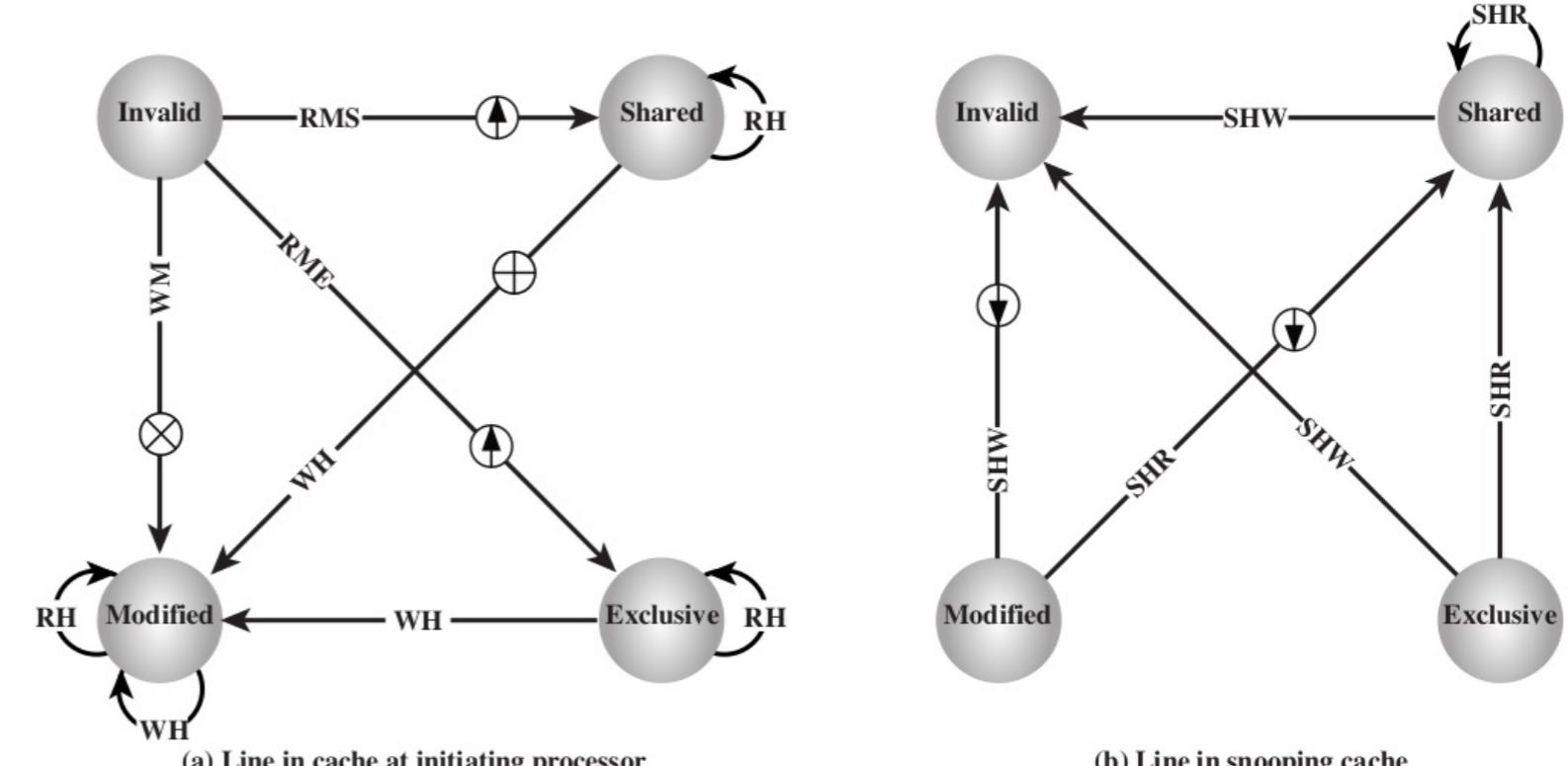

# Multiprocessadores Simétricos (SMP): coerência de cache: protocolo MESI

|                                  | M<br>Modificada           | E<br>Exclusiva            | S (shared)<br>Compartilhada              | I<br>Inválida                     |

|----------------------------------|---------------------------|---------------------------|------------------------------------------|-----------------------------------|

| Essa linha da cache está válida? | Sim                       | Sim                       | Sim                                      | Não                               |

| A cópia da memória está...       | desatualizada             | válida                    | válida                                   | —                                 |

| Há cópias em outras caches?      | Não                       | Não                       | Talvez                                   | Talvez                            |

| Uma escrita nessa linha...       | não vai para o barramento | não vai para o barramento | vai para o barramento e atualiza a cache | vai diretamente para o barramento |

|     |                                                  |                              |

|-----|--------------------------------------------------|------------------------------|

| RH  | Read hit                                         | ↓ Dirty line copyback        |

| RMS | Read miss, shared                                | ⊕ Invalidate transaction     |

| RME | Read miss, exclusive                             | ⊗ Read-with-intent-to-modify |

| WH  | Write hit                                        | ↑ Cache line fill            |

| WM  | Write miss                                       |                              |

| SHR | Snoop hit on read                                |                              |

| SHW | Snoop hit on write or read-with-intent-to-modify |                              |

## Referência e Leitura Adicional

### Capítulo 17: Processamento Paralelo

- 17.1 Organizações de múltiplos processadores

- 17.2 Multiprocessadores simétricos

- 17.3 Coerência de cache e protocolo MESI